# **Chapter 1 General Concepts**

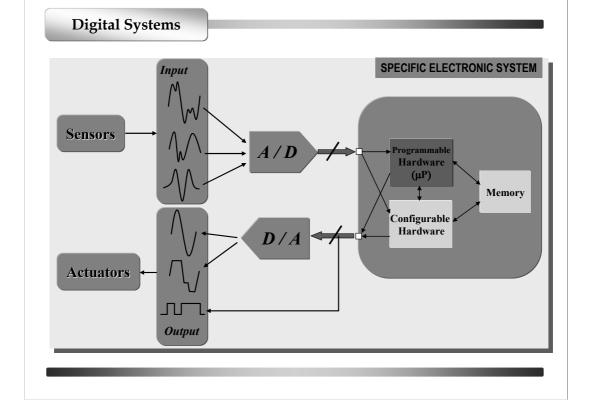

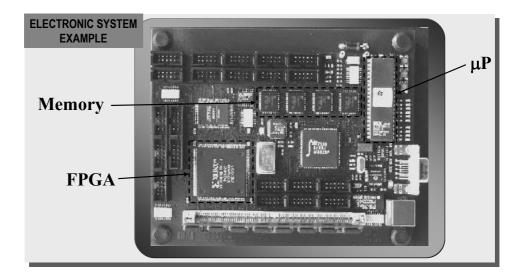

In an lectronic system we find different components:

- 1. Elements interfacing with physical world: Sensors and actuators

- 2. Elements transforming physical magnitudes (analog and continuous) into digital (discrete) :  $\underline{A/D}$  and  $\underline{D/A}$  converters

- 3. Elements that control the system and process variables: <u>Microprocessors and configurable logic elements</u>

- 4. Elements in charge of storing programs and variables: Memory

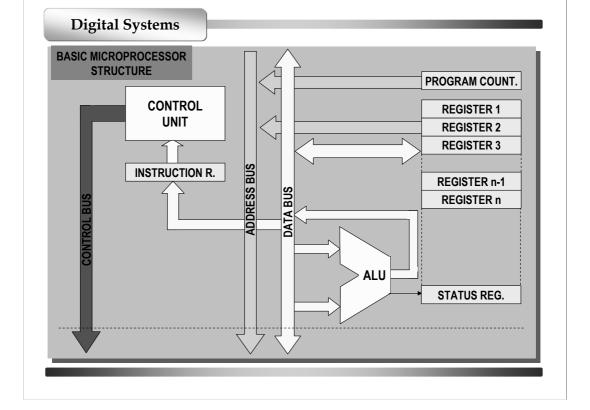

In a Microprocessor structure we have:

- 1. Subsystem implementing the state machine: Control unit

- 2. Local storage elements:

Dedicated registers (IR, PC i SR)

General purpose registers (R1...Rn)

- 3. Arithmetic-Logic unit: <u>ALU</u>

- 4. Interconnection elements: <u>Busses</u>

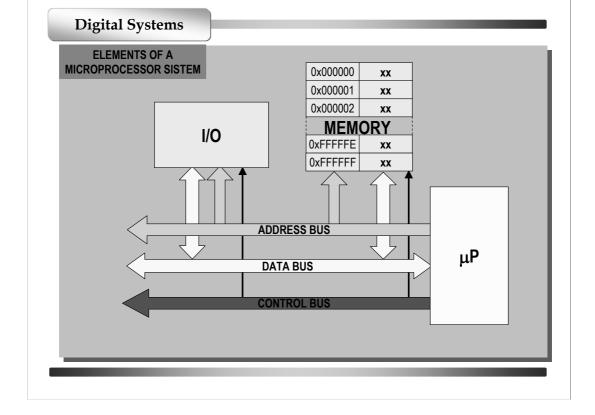

Microprocessador comunicates with external elements by means of three Sub-Busses

#### 1. ADDRESS BUS.

Defines the address space accessible by the microprocessor. Every accessible element has to be within that space.

## 2. DATA BUS.

These lines are used to move data elements (instructions and operands) between the microprocessor and external elements.

## 3. CONTROL BUS.

Contains all the timing, synchronization and control signals.

Two kind of external elements:

### 1. MEMORY

Contains all the information (program and data) relative to the application(s) running in the system.

#### 2. I/O

Implements the interface between the microprocessor and the physical world (periferals)

## **INSTRUCTION PHASES**

- 1. Fetch instruction code (R)

- 2. Instruction Decoding (I)

- 3. Operand(s) fetch (R)

- 4. Operate (I)

- 5. Result write-back (W)

## Instruction phases:

1. Fetch instruction code

PC > ADDRESS BUS.

DATA BUS > IR

One or more READ machine cycles

2. Instruction decoding

CONTROL UNIT decyphers instruction code.

Internal OPERATION

3. Read operand(s)

PC or Rx > ADDRESS BUS

DATA BUS > Rx

One or more READ machine cycles

4. Operate

iNTERNAL OPERATION (ALU)

5. Result(s) Write-back

PC or Rx > ADDRESS BUS

Rx > DATA BUS

One or more WRITE machine cycles

# MICROPROCESSOR MODELS

× SOFTWARE

× REGISTER SET

× ADDRESSING MODES

× INSTRUCTION SET

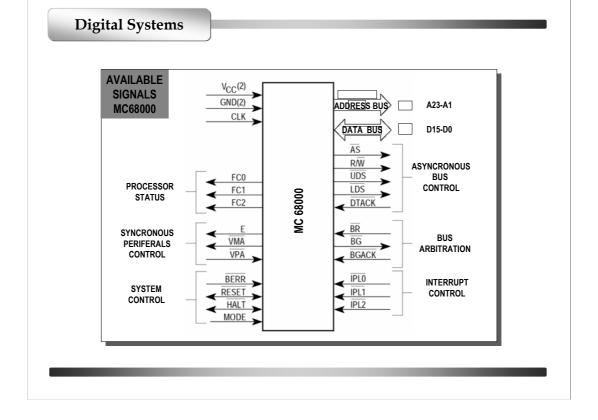

× HARDWARE

× AVAILABLE SIGNALS

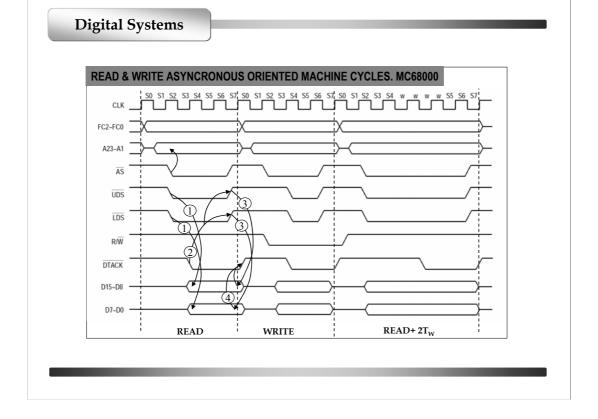

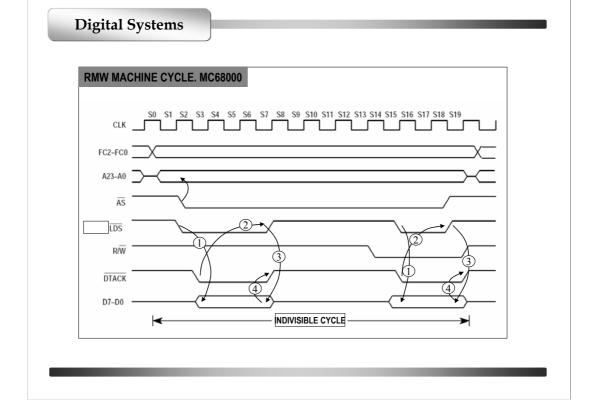

× MACHINE CYCLES

To use a microprocessor in a given applicartion we don't need to know its detailed. A symplified MODEL will suffice:

For application programming: SOFTWARE MODEL

REGISTER Set: Where can we (temporary) store our objects? INSTRUCTION Set: What can we do with different objects?

ADDRESSING Modes: How can we have access to different objects?

To build the system: HARDWARE MODEL

SIGNALS available: What signals can we connect?

MACHINE CYCLES: What is the temporal relationship between different signals? All that information is made available by manufacturer through operation manuals.

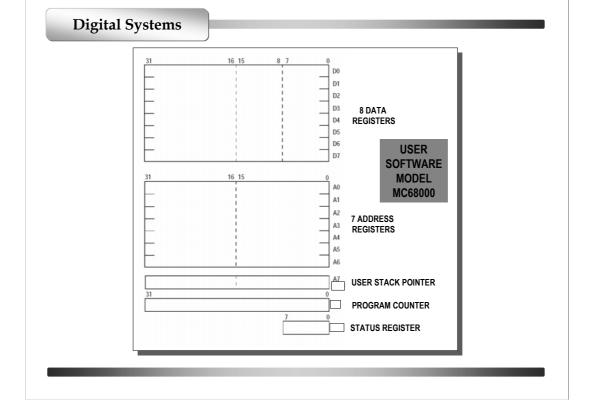

MC68000 (Motorola, Philips...)

8 ADDRESS REGISTERS (pointers)

8 DATA REGISTERS (general purpose)

1 PC (Instruction address)

1 SR (Operation FLAGS)

Of the 8 address registers, A7 és the STACK POINTER of user data structures, and some instructions make an IMPLICIT reference to it (PEA, LINK, UNLK...)

Any <ea> (EFFECTIVE ADRESS) using a REGISTER has to use an ADDRESS REGISTER

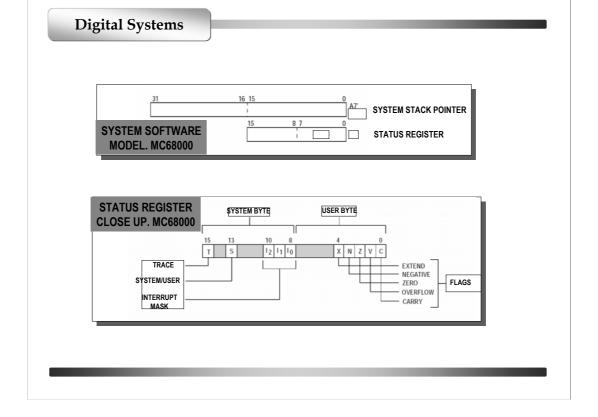

The SR (Status register) contains the FLAGS corresponding to the last OPERATION in the ALU. However, they can be used or modified at any time.

In SUPERVISOR MODE, apart from user registers we have:

A second STACK POINTER

A CONTROL REGISTER

## μP ADDRESSING MODES

1. IMPLICIT

Operand implicit in I.C.

2. IMMEDIATE

Operand included in I.C.

3. ABSOLUTE

Address included in I.C.

4. DIRECT

Operand in a Register

5. INDIRECT

Address in a Register

6. RELATIVE

Address as the sum of:

- **★**A register and an offset

- **★**Two registrers and an offset

| ADDRESSING MODES. MC68000                                                                                                                                                                                                                                                                                                                      |                                                       |                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|

| Mode                                                                                                                                                                                                                                                                                                                                           | Generation                                            | Syntax                                           |

| Register Direct Addressing Data Register Direct Address Register Direct                                                                                                                                                                                                                                                                        | EA=Dn<br>EA=An                                        | Dn<br>An                                         |

| Absolute Data Addressing Absolute Short Absolute Long                                                                                                                                                                                                                                                                                          | EA = (Next Word)<br>EA = (Next Two Words)             | (xxx).W<br>(xxx).L                               |

| Program Counter Relative<br>Addressing<br>Relative with Offset<br>Relative with Index and Offset                                                                                                                                                                                                                                               | EA = (PC)+d <sub>16</sub><br>EA = (PC)+d <sub>8</sub> | (d <sub>16</sub> ,PC)<br>(d <sub>8</sub> ,PC,Xn) |

| Register Indirect Addressing Register Indirect Postincrement Register Indirect Predecrement Register Indirect Register Indirect with Offset Indexed Register Indirect with Offset                                                                                                                                                              | EA = (An)<br>EA = (An), An \(                         | (An)<br>(An)+<br>-(An)<br>(d16.An)<br>(d8,An,Xn) |

| Immediate Data Addressing<br>Immediate<br>Quick Immediate                                                                                                                                                                                                                                                                                      | DATA = Next Word(s)<br>Inherent Data                  | # <data></data>                                  |

| Implied Addressing□<br>Implied Register                                                                                                                                                                                                                                                                                                        | EA = SR. USP. SSP. PC.                                | SR,USP,SSP,PC,                                   |

| EA = Effective Address PC = Program Counter Dn = Data Register An = Address Register (1) = Contents of Contents of PC = Program Counter (1) = PC = P |                                                       | User Stack Pointer                               |

See MC68000 PROGRAMMER'S REFERENCE MANUAL:

2.2 EFFECTIVE ADRESSING MODES

| nstruction              | Operand Syntax                                                                                                | Operand Size                                                | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXG                     | Rn, Rn                                                                                                        | 32                                                          | $Rn \leftarrow \rightarrow Rn$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FMOVE                   | FPm,FPn<br><ea>,FPn<br/>FPm,<ea><br/><ea>,FPcr<br/>FPcr,<ea></ea></ea></ea></ea>                              | X<br>B, W, L, S, D, X, P<br>B, W, L, S, D, X, P<br>32<br>32 | Source → Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FSMOVE,<br>FDMOVE       | FPm,FPn<br><ea>,FPn</ea>                                                                                      | X<br>B, W, L, S, D, X                                       | Source $\rightarrow$ Destination; round destination to single or double precision.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FMOVEM                  | <ea>,<list><sup>1</sup><br/><ea>,Dn<br/><list><sup>1</sup>,<ea><br/>Dn,<ea></ea></ea></list></ea></list></ea> | 32, X<br>X<br>32, X<br>X                                    | Listed Registers → Destination  Source → Listed Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LEA                     | <ea>,An</ea>                                                                                                  | 32                                                          | <ea> → An</ea>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LINK                    | An,# <d></d>                                                                                                  | 16, 32                                                      | $SP - 4 \rightarrow SP$ ; $An \rightarrow (SP)$ ; $SP \rightarrow An$ , $SP + D \rightarrow SP$                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MOVE<br>MOVE16<br>MOVEA | <ea>,<ea><br/><ea>,<ea><br/><ea>,An</ea></ea></ea></ea></ea>                                                  | 8, 16, 32<br>16 bytes<br>16, 32 → 32                        | Source → Destination<br>Aligned 16-Byte Block → Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MOVEM                   | list, <ea><br/><ea>,list</ea></ea>                                                                            | 16, 32<br>16, 32 → 32                                       | Listed Registers → Destination Source → Listed Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MOVEP                   | Dn, (d <sub>16</sub> ,An)<br>(d <sub>16</sub> ,An),Dn                                                         | 16, 32                                                      | $\begin{array}{l} \text{Dn } 31\text{-}24 \rightarrow (\text{An + d}_n); \text{ Dn } 23\text{-}16 \rightarrow (\text{An + d}_n + 2); \\ \text{Dn } 15\text{-}8 \rightarrow (\text{An + d}_n + 4); \text{ Dn } 7\text{-}0 \rightarrow (\text{An + d}_n + 6) \\ (\text{An + d}_n) \rightarrow \text{Dn } 31\text{-}24; (\text{An + d}_n + 2) \rightarrow \text{Dn } 23\text{-}16; \\ (\text{An + d}_n + 4) \rightarrow \text{Dn } 15\text{-}8; (\text{An + d}_n + 6) \rightarrow \text{Dn } 7\text{-}0 \end{array}$ |

| MOVEQ                   | # <data>,Dn</data>                                                                                            | 8 → 32                                                      | Immediate Data → Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PEA                     | <ea></ea>                                                                                                     | 32                                                          | $SP-4 \rightarrow SP$ ; $\leq ea \geq \rightarrow (SP)$                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| UNLK                    | An                                                                                                            | 32                                                          | $An \rightarrow SP$ ; $(SP) \rightarrow An$ ; $SP + 4 \rightarrow SP$                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Instruction  | Operand Syntax                                                        | Operand Size                                                                                                          | Operation                                               |  |

|--------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| ADD          | Dn, <ea><br/><ea>,Dn</ea></ea>                                        | 8, 16, 32<br>8, 16, 32                                                                                                | Source + Destination → Destination                      |  |

| ADDA         | <ea>,An</ea>                                                          | 16, 32                                                                                                                |                                                         |  |

| ADDI<br>ADDQ | # <data>,<ea><br/>#<data>,<ea></ea></data></ea></data>                | 8, 16, 32<br>8, 16, 32                                                                                                | Immediate Data + Destination → Destination              |  |

| ADDX         | Dn,Dn<br>-(An), -(An)                                                 | 8, 16, 32<br>8, 16, 32                                                                                                | Source + Destination + X → Destination                  |  |

| CLR          | <ea></ea>                                                             | 8, 16, 32                                                                                                             | 0 → Destination                                         |  |

| CMP<br>CMPA  | <ea>,Dn<br/><ea>,An</ea></ea>                                         | 8, 16, 32<br>16, 32                                                                                                   | Destination – Source                                    |  |

| CMPI         | # <data>,<ea></ea></data>                                             | 8, 16, 32                                                                                                             | Destination - Immediate Data                            |  |

| CMPM         | (An)+,(An)+                                                           | 8, 16, 32                                                                                                             | Destination - Source                                    |  |

| CMP2         | <ea>,Rn</ea>                                                          | 8, 16, 32                                                                                                             | Lower Bound → Rn → Upper Bound                          |  |

| DIVS/DIVU    | <ea>,Dn<br/><ea>,Dr-Dq<br/><ea>,Dq<br/><ea>,Dr-Dq</ea></ea></ea></ea> | $32 + 16 \rightarrow 16,16$<br>$64 + 32 \rightarrow 32,32$<br>$32 + 32 \rightarrow 32$<br>$32 + 32 \rightarrow 32,32$ | (Signed or Unsigned Quotient, Remainder)                |  |

| EXT<br>EXTB  | Dn<br>Dn<br>Dn                                                        | 8 → 16<br>16 → 32<br>8 → 32                                                                                           | Sign-Extended Destination $\rightarrow$ Destination     |  |

| MULS/MULU    | <ea>,Dn<br/><ea>,Dl<br/><ea>,Dh–Dl</ea></ea></ea>                     | 16 x 16 → 32<br>32 x 32 → 32<br>32 x 32 → 64                                                                          | Source x Destination → Destination (Signed or Unsigned) |  |

| NEG          | <ea></ea>                                                             | 8, 16, 32                                                                                                             | 0 – Destination → Destination                           |  |

| NEGX         | <ea></ea>                                                             | 8, 16, 32                                                                                                             | 0 – Destination – X → Destination                       |  |

| SUB          | <ea>,Dn<br/>Dn,<ea></ea></ea>                                         | 8, 16, 32<br>8, 16, 32                                                                                                | Destination = Source → Destination                      |  |

| SUBA         | <ea>,An</ea>                                                          | 16, 32                                                                                                                |                                                         |  |

| SUBI<br>SUBQ | # <data>,<ea><br/>#<data>,<ea></ea></data></ea></data>                | 8, 16, 32<br>8, 16, 32                                                                                                | Destination – Immediate Data → Destination              |  |

| SUBX         | Dn,Dn<br>-(An), -(An)                                                 | 8, 16, 32<br>8, 16, 32                                                                                                | Destination – Source – X → Destination                  |  |

| nstruction  | Operand Syntax                                        | x Operand S  |                | ize                                                     | Operation                                  |                                                                                                                          |

|-------------|-------------------------------------------------------|--------------|----------------|---------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| AND         | <ea>,Dn</ea>                                          |              | 8, 16, 32      |                                                         | So                                         | urce Λ Destination → Destination                                                                                         |

|             | Dn, <ea></ea>                                         |              | 8, 16, 32      |                                                         |                                            |                                                                                                                          |

| ANDI        | # <data>,<ea></ea></data>                             |              | 8, 16, 32      |                                                         | Immediate Data ∧ Destination → Destination |                                                                                                                          |

| EOR         | Dn, <ea></ea>                                         |              | 8, 16, 32      |                                                         | Source ⊕ Destination → Destination         |                                                                                                                          |

| EORI        | # <data>,<ea></ea></data>                             |              | 8, 16, 32      |                                                         | Immediate Data ⊕ Destination → Destination |                                                                                                                          |

| NOT         | <ea></ea>                                             |              | 8, 16, 32      | :                                                       | ~ Destination → Destination                |                                                                                                                          |

| OR          | <ea>,Dn<br/>Dn,<ea></ea></ea>                         |              | 8, 16, 32      |                                                         | So                                         | urce V Destination → Destination                                                                                         |

| ORI         | # <data>,<ea></ea></data>                             |              | 8, 16, 32      |                                                         | lm                                         | mediate Data $V$ Destination $\rightarrow$ Destination                                                                   |

| Instruction | Operand Synta                                         | x Operan     |                | d Size                                                  | 9                                          | Operation                                                                                                                |

| BCHG        | Dn, <ea><br/>#<data>,<ea></ea></data></ea>            | 8, 3         |                |                                                         |                                            | ~ ( <bit number=""> of Destination) <math>\rightarrow</math> Z <math>\rightarrow</math> Bit of Destination</bit>         |

| BCLR        | Dn, <ea><br/>#<data>,<ea></ea></data></ea>            |              | 8, 32<br>8, 32 |                                                         |                                            | $\sim$ ( <bit number=""> of Destination) <math>\rightarrow</math> Z; <math>0 \rightarrow</math> Bit of Destination</bit> |

| BSET        | Dn, <ea><br/>#<data>,<ea></ea></data></ea>            |              | 8, 32<br>8, 32 |                                                         |                                            | $\sim$ ( <bit number=""> of Destination) <math>\rightarrow</math> Z; 1 <math>\rightarrow</math> Bit of Destination</bit> |

| BTST        | Dn, <ea><br/>#<data>,<ea></ea></data></ea>            | 8, 3<br>8, 3 |                |                                                         |                                            | ~ ( <bit number=""> of Destination) <math display="inline">\to Z</math></bit>                                            |

| Instruction | Operand Syntax                                        | Operand Size |                |                                                         |                                            | Operation                                                                                                                |

| ABCD        | Dn,Dn<br>-(An), -(An)                                 | 8            |                | Sourc                                                   | e <sub>10</sub>                            | + Destination $_{10}$ + X $\rightarrow$ Destination                                                                      |

| NBCD        | <ea></ea>                                             | 8            |                | 0 – De                                                  | esti                                       | nation <sub>10</sub> – X → Destination                                                                                   |

| PACK        | -(An), -(An) # <data><br/>Dn,Dn,#<data></data></data> |              |                | Unpackaged Source + Immediate Data → Packed Destination |                                            |                                                                                                                          |

| SBCD        | Dn,Dn<br>-(An), -(An)                                 | 8            |                | Destin                                                  | atio                                       | on <sub>10 −</sub> Source <sub>10 −</sub> X → Destination                                                                |

| UNPK        | -(An),-(An) # <data></data>                           | 8 → 16 Unpa  |                | Packe                                                   | d S                                        | Source → Unpacked Source                                                                                                 |

|             | Dn,Dn,# <data></data>                                 |              |                |                                                         |                                            | d Source + Immediate Data →<br>ed Destination                                                                            |

| nstruction                              | Operand Synta:        | Operand Size         | Operation                                                                                 |  |  |

|-----------------------------------------|-----------------------|----------------------|-------------------------------------------------------------------------------------------|--|--|

|                                         |                       | Integer and Floating | ng-Point Conditional                                                                      |  |  |

| Bcc, FBcc                               | <label></label>       | 8, 16, 32            | If Condition True, Then PC + d <sub>n</sub> → PC                                          |  |  |

| DBcc, FDBcc                             | Dn, <label></label>   | 16                   | If Condition False, Then $Dn-1 \to Dn$<br>If $Dn \to -1$ , Then $PC + d_n \to PC$         |  |  |

| Scc, FScc                               | <ea></ea>             | 8                    | If Condition True, Then 1's → Destination;<br>Else 0's → Destination                      |  |  |

|                                         |                       | Uncor                | nditional                                                                                 |  |  |

| BRA                                     | <label></label>       | 8, 16, 32            | $PC + d_n \rightarrow PC$                                                                 |  |  |

| BSR                                     | <label></label>       | 8, 16, 32            | $SP - 4 \rightarrow SP$ ; $PC \rightarrow (SP)$ ; $PC + d_n \rightarrow PC$               |  |  |

| JMP                                     | <ea></ea>             | none                 | Destination → PC                                                                          |  |  |

| JSR                                     | <ea></ea>             | none                 | $SP - 4 \rightarrow SP$ ; $PC \rightarrow (SP)$ ; Destination $\rightarrow PC$            |  |  |

| NOP                                     | none                  | none                 | PC + 2 → PC (Integer Pipeline Synchronized)                                               |  |  |

| FNOP                                    | none                  | none                 | PC + 4 → PC (FPU Pipeline Synchronized)                                                   |  |  |

|                                         |                       | Re                   | turns                                                                                     |  |  |

| RTD                                     | # <data></data>       | 16                   | $(SP) \rightarrow PC$ ; $SP + 4 + d_n \rightarrow SP$                                     |  |  |

| RTR                                     | none                  | none                 | $(SP) \rightarrow CCR; SP + 2 \rightarrow SP; (SP) \rightarrow PC; SP + 4 \rightarrow SR$ |  |  |

| RTS                                     | none                  | none                 | $(SP) \rightarrow PC; SP + 4 \rightarrow SP$                                              |  |  |

|                                         |                       |                      | and Scc specify testing one of the following conditions:                                  |  |  |

| CC—Carry clear GE—Greater than or equal |                       | qual                 |                                                                                           |  |  |

| LS—Lower or same PL—Plus                |                       | PL—Plus              |                                                                                           |  |  |

| CS—Carry set GT—Greater than            |                       | GT—Greater than      |                                                                                           |  |  |

| LT—Less than T—Always true*             |                       | T—Always true*       |                                                                                           |  |  |

| EQ—Equal HI—Higher                      |                       | HI—Higher            |                                                                                           |  |  |

| MI—Minus VC—Overflow clear              |                       | /C—Overflow clear    |                                                                                           |  |  |

| F—Never true* LE—Less than or equal     |                       | LE—Less than or equa | ıl                                                                                        |  |  |

| NE—Not ec                               |                       | VS—Overflow set      |                                                                                           |  |  |

|                                         | o the Bcc instruction |                      |                                                                                           |  |  |

#### **Digital Systems** MEMORY DATA BIT DATA 1 BYTE = 8 BITS **ORGANIZATION** MC68000 INTEGER DATA 1 BYTE = 8 BITS 1 LONG WORD = 2 WORDS = 4 BYTES = 32 BITS L BYTE 0 BYTE 0 HIGH-ORDER WORD BYTE 1 LONG WORD 0 ADDRESSES BYTE 2 BYTE 2 LOW-ORDER \_ WORD BYTE 3 BYTE 3 BYTE 0 1 WORD = 2 BYTES = 16 BITS HIGH-ORDER . WORD BYTE 1 BYTE 0 (MS BYTE) LONG WORD 1 BYTE 1 (LS BYTE) BYTE 2 LOW-ORDER BYTE 3 BYTE 0 (MS BYTE) Н WORD 1 -BYTE 1 (LS BYTE)