### • VHDL-based design and synthesis

- 1. Description of basic primitives

- 2. Behavioral models of systems

- 3. The standard synthesis package IEEE Std 1076.3-1997

- 4. The VHDL RTL synthesis standard IEEE Std 1076.6-1999

## 1. Description of basic primitives

- Concurrent assignments and processes:

- Concurrent assignments: A change is projected onto the signal placed on the left hand side of the assignment whenever there is a change on the signals placed on the right hand side a <= b xor c;

➤ **Processes:** The changes on the signals take place when the is resumed and before its next activation. The activation of a process is a consequence of changes in signals

## General description rules:

- **Combinational logic:**

- Concurrent assignments (recommended)

- Processes (sensitivity list, default case)

- > Sequential logic:

- Processes with wait primitive ⇒ Flipflops

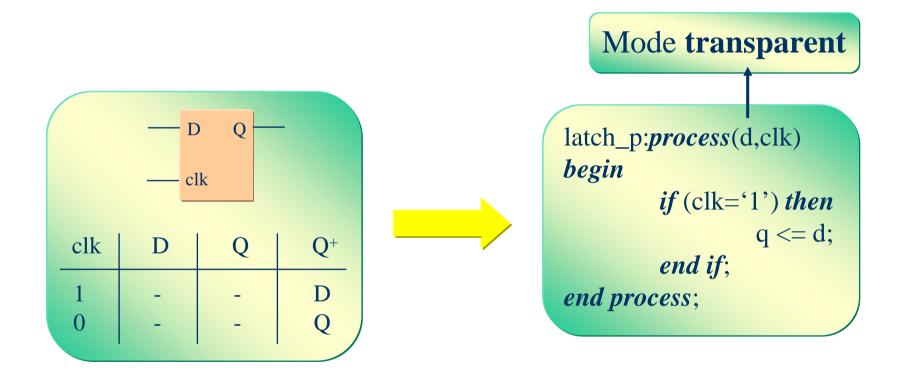

- Processes with sensitivity list ⇒ Latches

## • Description of combinational logic:

## • Feedback in concurrent assignments:

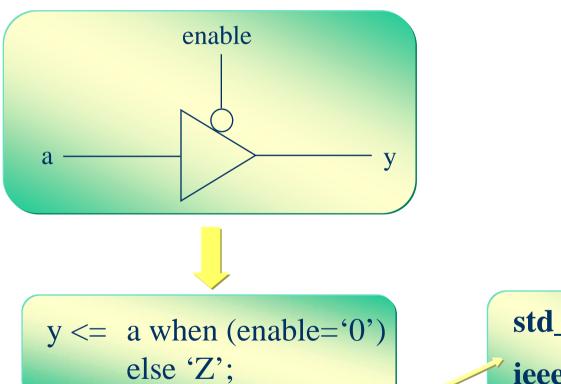

## • Tri-state buffers:

std\_logic type

ieee library

- Description of sequential logic:

- **Definition of clock signals:**

```

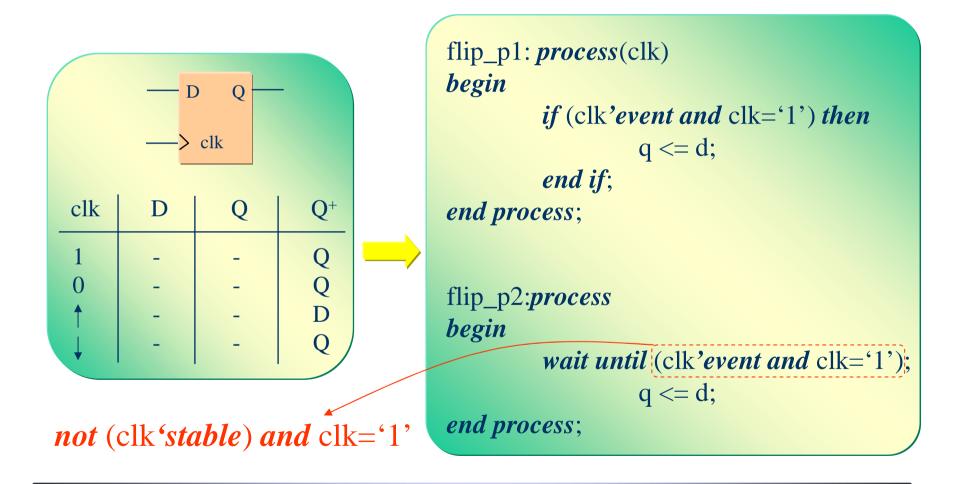

➤ Wait primitive:

not clk'stable and clk='1'

process

begin

wait until (clk'event and clk='1');

> Sensitivity list (asynchronous control signals):

process(clk)

begin

if (clk'event and clk='1')

```

## • Multiple clock signals:

```

m_clock: process(clk)

begin

if (clk'event and clk='0') then

q <= a;

elsif (clk'event and clk='1') then

q <= b;

end if;

end process;

```

## • Sequential primitives active by level (latches):

## • Sequential primitives active by edge (flipflops):

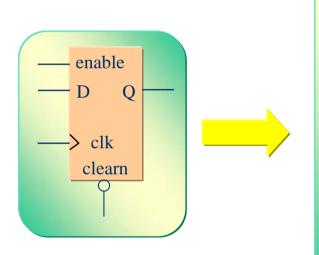

## • Control signals:

#### Asynchronous reset

```

async_flip: process(clk,clearn)

begin

if (clearn='0') then

q <= '0';

elsif (clk'event and clk='1') then

q <= d;

end if;

end process;

```

#### Synchronous reset

```

sync_flip: process

begin

wait until (clk'event and clk='0');

if (clearn='0') then

q <= '0';

else

q <= d;

end if;

end process;</pre>

```

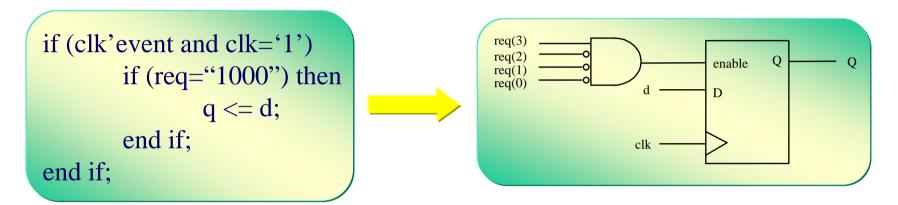

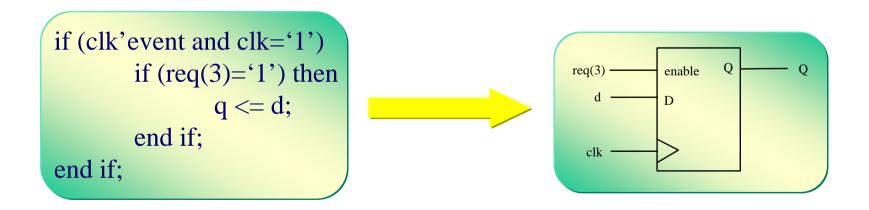

## • E-type register (enable):

```

E_flipflop: process

begin

wait until (clk'event and clk='1');

if (clearn='0') then

Q <= '0';

elsif (enable='1') then

Q <= D;

end if;

end process;

```

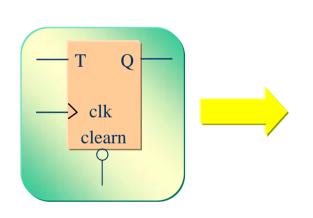

## • T-type register (toggle):

```

T_flipflop: process

begin

wait until (clk'event and clk='1');

if (clearn='0') then

Q <= '0';

elsif (T='1') then

Q <= not Q;

end if;

end process;

```

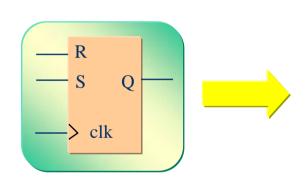

## • RS-type register (Reset/Set):

```

RS_flipflop: process

begin

wait until (clk'event and clk='1');

if (R='1') then

Q <= '0';

elsif (S='1') then

Q <= '1';

end if;

end process;

```

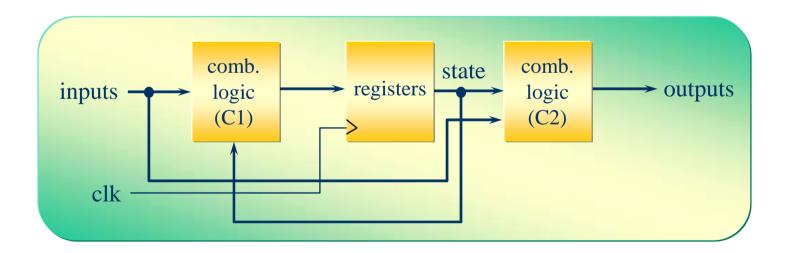

#### • Finite state machines:

- > Systems with finite memory (number of states)

- The state of the system and its outputs depend on its previos state and its inputs

### • Structure of a finite state machine:

```

architecture description of fsm is

type state is (s0, s\overline{1}, ..., sn);

signal current_state, future_state: state;

begin

future_state <= s0 when (inputs="..." and current_state="...")

else s1 when ...

else ...;

registers: process

begin

wait until (clk'event and clk='1');

if (clearn='0') then

current state <= s0;

else

current state <= future state;

end if;

end process;

"..." when (inputs="..." and current_state="...")

outputs <=

else "..." when ...

else ...;

```

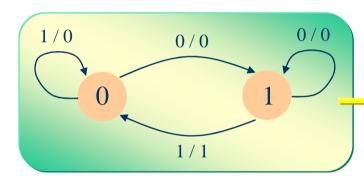

## • Example: Detector for the sequence "01"

```

architecture fsm of detector is

type state is (s0, s1);

signal current_state, future_state: state;

begin

future_state <= s0 when (data_in='1')

else s1:

registers: process

begin

wait until (clk'event and clk='1');

if (clearn='0') then

current state <= s0;

else

current_state <= future_state;</pre>

end if;

end process;

detect <= '1' when ((current_state=s1) and</pre>

(data_in='1'))

else '0':

end fsm;

```

### 2. Behavioral models of systems

Variables vs Signals

#### Signals

- > Declared in architecture

- > Assignment with delay

- Updated at the end of a process

- > Slow simulation

#### **Variables**

- Declared in process, block, function, procedure

- > Assignment without delay

- Updated immmediatley

- > Fast simulation

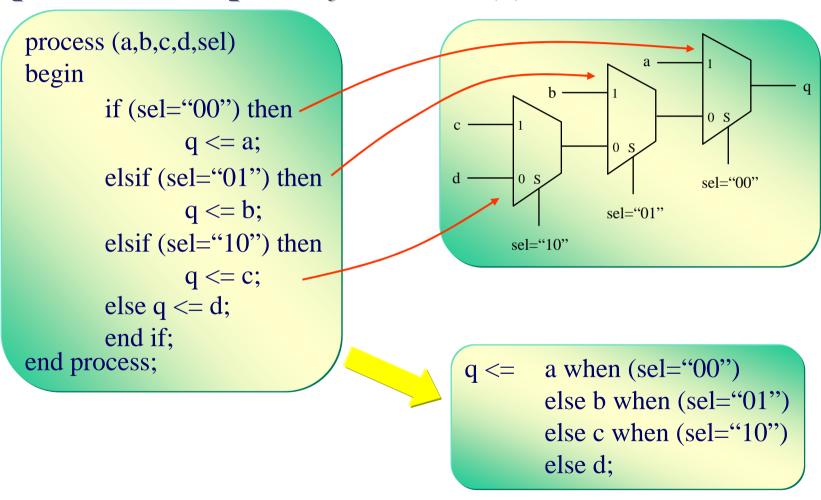

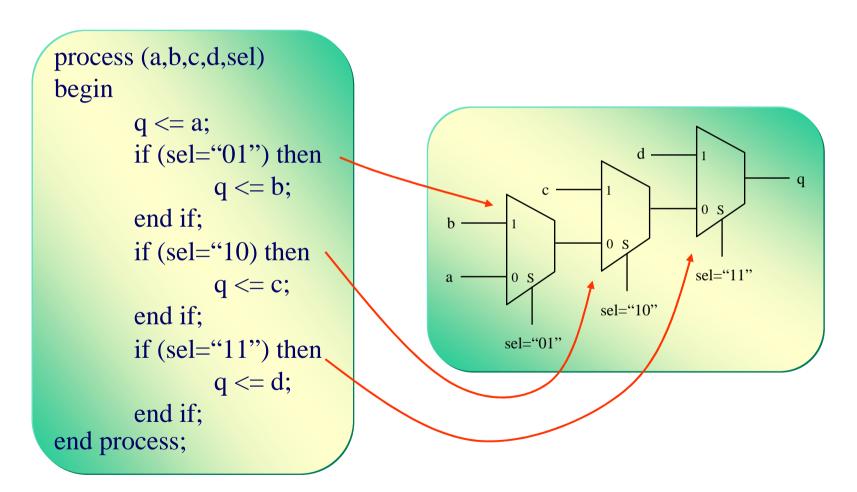

# • If primitive as a priority encoder (I):

## • If primitive as a priority encoder (II):

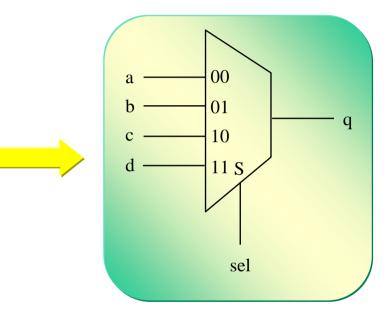

## • Case primitive as a multiplexer:

```

\begin{array}{c} process~(a,b,c,d,sel)\\ begin\\ case~sel~is\\ when~`00"=>q<=a;\\ when~`01"=>q<=b;\\ when~`10"=>q<=c;\\ when~others=>q<=d;\\ end~case;\\ end~process; \end{array}

```

- Case: Complex decoding

- If: Selection with critical delay

with sel select

q <= a when "00",

b when "01",

c when "10",

d when others;

### • Incomplete decoding:

### • Signals with critical delay:

```

if (clk'event and clk='1') then

if (crtica='1' and no_critica='1') then

o \le in1;

else

o \le in2;

end if;

end if;

if (clk'event and clk='1') then

if (crtica='1') then

if (no_critica='1') then

o \le in1;

else

o \le in2;

end if;

end if;

end if;

```

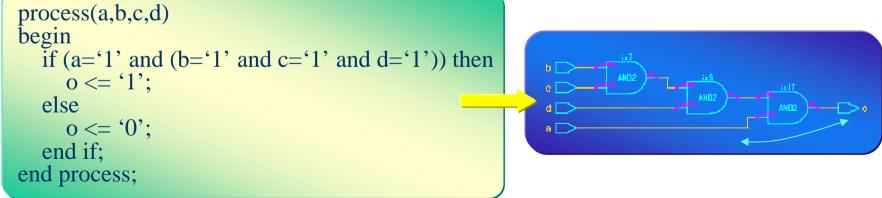

### • Latch inference (I):

```

process(a,b,c,d)

begin

if (a='1' and b='1' and c='1' and d='1') then

o <= '1';

else

o <= '0';

end if;

end process;

process(a,b,c,d)

begin

if (a='1') then

if (b='1' and c='1' and d='1') then

o <= '1';

else

o \le 0';

end if;

end if;

end process;

```

## • Latch inference (II):

```

process(a,b,c,d)

begin

if (a='1' and b='1' and c='1' and d='1') then

o <= '1';

else

o <= '0';

end if;

end process;

process(a,b,c,d)

begin

if (a='1') then

if (b='1' and c='1' and d='1') then

o <= '1';

end if;

else

o <= '0';

end if;

end process;

```

## • Priority for critical signals (I):

```

process(a,b,c,d)

begin

if (a='1' and b='1' and c='1' and d='1') then

o <= '1':

else

o <= '0';

end if;

end process;

process(a,b,c,d)

begin

if (a='1') then

if (b='1' and c='1' and d='1') then

o <= '1';

else o <= '0';

end if;

else

o <= '0';

end if;

end process;

```

## • Priority for critical signals (II):

```

process(a,b,c,d)

begin

if (a='1' and b='1' and c='1' and d='1') then

o <= '1';

else

o <= '0';

end if;

end process(a,b,c,d)

process(a,b,c,d)

```

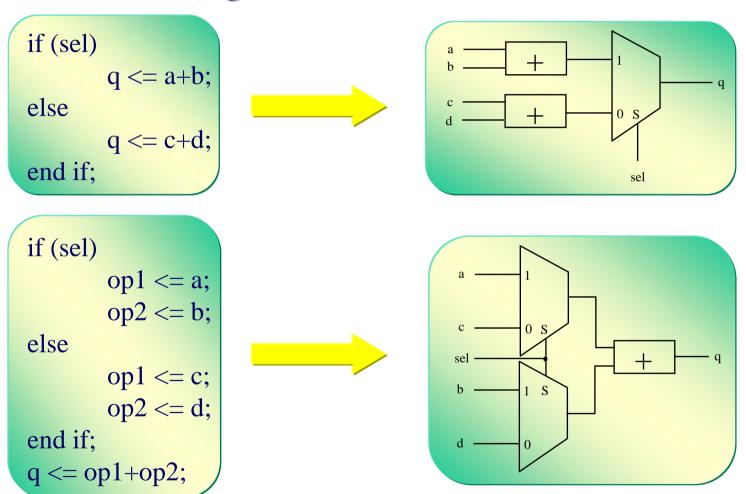

## • Resource sharing:

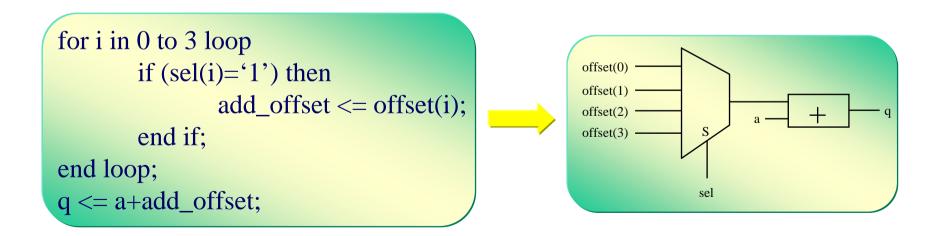

## • Scheduling of operations:

> sel1, sel2 mutually exclusive

```

if (sel1) then q \le a+b; elsif (sel2) then q \le a+c; end if;

```

- 1 control level

- 1 adder

```

if (sel1) then q <= a+b; else if (sel2) then \\ q <= a+c; end if; end if;

```

- 1-2 control levels

- 1 adder

- 3-4 control levels

- 1-2 adders

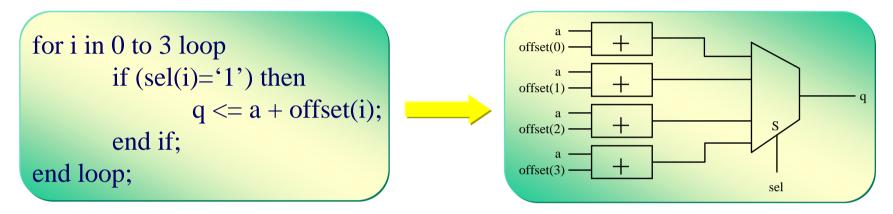

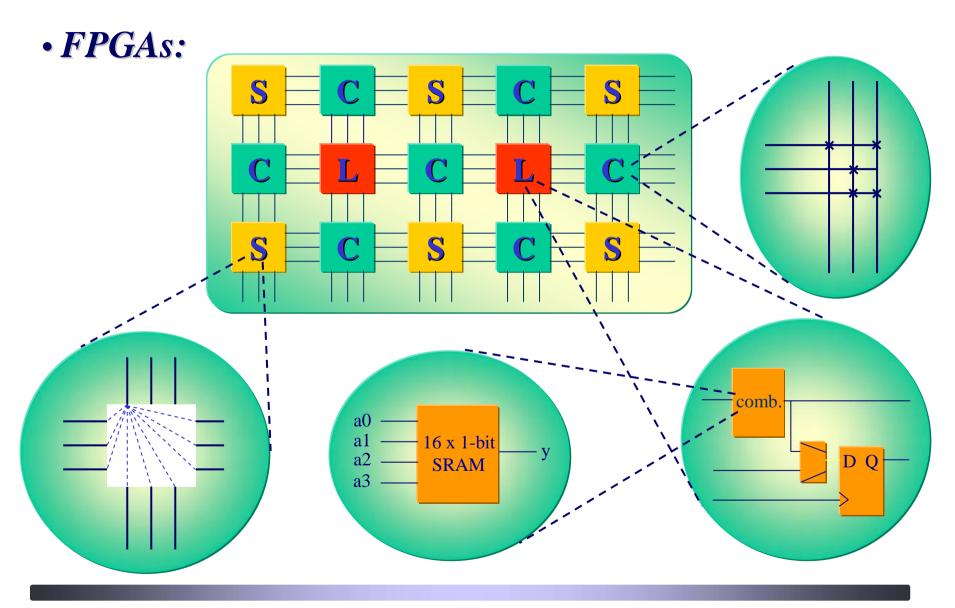

### • Operations inside loops:

## • Loop expansion:

$$q \leftarrow ((initial\_value+inc(0)) + (inc(1)+inc(2)));$$

$$inc(1) + inc(2) + q$$

$$inc(1) + q$$

2. Behavioral models of systems

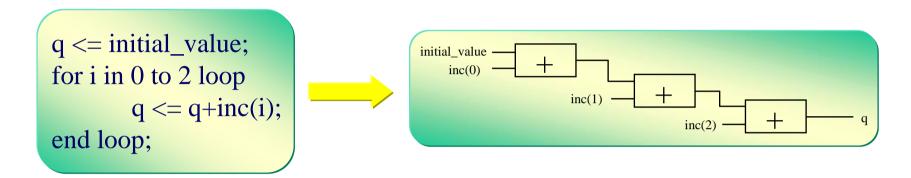

## • Synthesis principles for FPGAs:

- **Limited resources:**

- combinational elements

- sequential elements

- connectivity

- **Execution delay:**

$$t_{total} = t_{component} + t_{routing} + t_{switch}$$

$t_{routing}, t_{switch} >> t_{component},$  and unknown before the physical design (P & R)

Values to minimise

- Minimisation of the connectivity delay:

- **➤** Use specific hardware macros:

- > Adders / subtractors

- > Shifters / rotators

- **Counters**

- Shift registers

- Memory blocks

- **➤** One-hot encoding for finite state machines

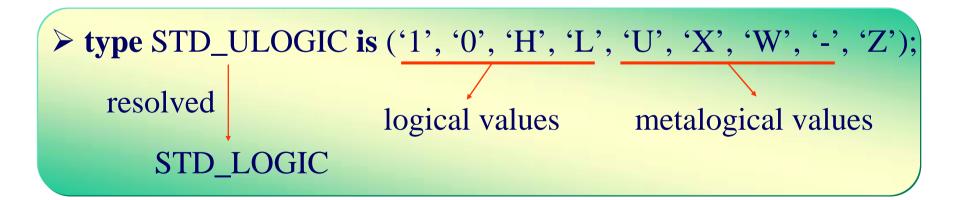

# 3. The standard synthesis package IEEE 1076.3-97

- ➤ Interpretation for synthesis of the types *BIT*, *BOOLEAN* and *STD\_ULOGIC*

- ➤ Definition of the function *STD\_MATCH*

- > Definition of functions to handle signal edges

- ➤ Definition of function for representing signed and unsigned values, as well as conversion functions between types

#### • Interpretation of logical values:

- > Interpretation as a value 0:

- The value '0' of type BIT

- The value FALSE of type BOOLEAN

- The values '0' and 'L' of type STD\_ULOGIC

- ➤ Interpretation as a value 1:

- The value '1' of type BIT

- The value TRUE of type BOOLEAN

- The values '1' and 'H' of type STD\_ULOGIC

- Interpretation of metalogical values:

- ➤ Relational expressions: In an equality relation, if one operand is a metalogical value and the other is not a static value, the result should be the value FALSE

#### Interpretation of metalogical values:

- ➤ Case primitives: If a metalogical value occurs in a choice, the synthesis tool shall interpret the choice as one that can never occur

- ➤ Arithmetic, logic and shift operations: The synthesis tool shall treat the operation as an error

### • Interpretation of the high impedance ('Z') value:

- ➤ If the value 'Z' occurs in an assignment, the synthesis tool shall convert the assignment in a tri-state buffer

- ➤ If the value 'Z' occurs in any construction different from an assignment, the synthesis tool shall treat it as a metalogical value

#### • The STD-MATCH function:

- ➤ If this function is applied to two arguments of type STD\_ULOGIC, it will return the TRUE value if:

- Both values are well-defined and are the same, or

- One value is '0' and the other is 'L', or

- One value is '1' and the other is 'H', or

- At least one of the values is '-'

- ➤ If this function is applied to two arguments that are vectors of type STD\_ULOGIC, it will return the TRUE value if:

- The operands have the same length, and

- STD\_MATCH applied to each pair of matching elements returns TRUE

- Edge detection: rising\_edge(signal), falling\_edge(signal)

#### • Standard arithmetic packages:

- > NUMERIC\_BIT: Based on the BIT type

- > NUMERIC\_STD: Based on the STD\_LOGIC type

#### New types:

- > UNSIGNED: Unsigned interger, with the most significant bit on the left

- > **SIGNED:** Interger in 2's complement, with the most significant bit on the left

## 4. The VHDL RTL synthesis standard IEEE 1076.6-1999

- Approved on July de 1998 (IEEE Std 1076.6-1999)

- Motivation for VHDL: Modelling of electronic systems

Syntactic and semantic flexibility

Non-portable synthesis

- Impossible to cover the whole language

- Tool-dependent synthesis

- Motivation for a standard synthesis subset:

- > Portability between tools

> Design portability (specification language):

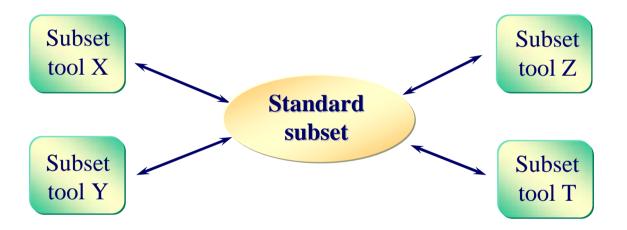

## • The VHDL RTL synthesis standard (IEEE 1076.6)

- RTL description:

- > Data transfer between memory elements (registers)

- Combinational logic

- Supported data types:

- ➤ BIT, BOOLEAN, BIT\_VECTOR, CHARACTER, STRING, INTEGER (1076-2000)

- ➤ STD\_ULOGIC, STD\_ULOGIC\_VECTOR, STD\_LOGIC, STD\_LOGIC\_VECTOR (1164-1993)

- ➤ SIGNED, UNSIGNED (1076.3-97)

- Sequential primitives active by edge (flipflops):

- ➤ Clock signal: Types BIT, STD\_ULOGIC, STD\_LOGIC

- > Specification of a clock (rising) edge:

- With the if statement:

- rising\_edge(clock)

- clock'event and clock='1'

- clock='1' and clock'event

- not clock'stable and clock='1'

- clock='1' and **not** clock**'stable**

- > Specification of a clock (rising) edge:

- With the wait until statement:

- rising\_edge(clock)

- clock='1'

- clock'event and clock='1'

- clock='1' and clock'event

- not clock'stable and clock='1'

- clock='1' and not clock'stable

- > Only one clock edge per process is allowed

- The wait until is not allowed within procedures

### • Modelling:

```

process(clock)

process

begin

begin

if (clock'event and clock='1') then

wait until (clock='1');

q \ll d;

q \ll d;

end if;

end process;

end process;

• One per process

process

• First statement

variable var: unsigned(3 downto 0);

begin

wait until (clock = '1');

Variable read before

var := var + 1;

being assigned

count <= var;

end process;

```

### Asynchronous control signals:

```

process(clk, set, reset)

begin

if (reset='1') then

Q <= '0';

elsif (set='1') then

Q <= '1';

elsif (clk'event and clk='1') then

Q \leq D;

end if;

end process;

```

# • Sequential primitives active by level (latches):

### > Necessary inference:

- One signal or variable is assigned in a process without definition of clock signals **and**

- There are executions of the process that do not imply an explicit assignment on the signal or variable

#### > Probable inference:

- One signal or variable is assigned in a process without definition of clock signals **and**

- There are executions of the process where the value of the signal or variable is read before it is assigned

- Tri-state buffers: Conditional assignment of the value 'Z' on a signal or variable

- Modelling of combinational logic:

- > Concurrent assignments

- Assignments within a process that take place with every execution of the process

- Meta-comments:

- -- RTL\_SYNTHESIS ON

- -- RTL\_SYNTHESIS OFF

• **ENUM\_ENCODING attribute:** Used to instruct the synthesis tools the coding to be used for the elements that constitute an enumerated type (finite state machines)

attribute ENUM\_ENCODING: string;

**type** state is (s0, s1, s2, s3);

attribute ENUM\_ENCODING of state: type is "0001 0010 0100 1000";